在AMD隆重推出其3D V-Cache Design之后,AMD已确认该技术将在明年初推出的Zen3的Ryzen CPU中导入。

AMD在解释这项技术方面做得很好,但没有说明哪些Zen CPU将率先採用该技术。他们的展示包括採用Zen3的Ryzen 9 5900X原型,该公司现已确认3D V-Cache晶片堆叠技术确实首先应用于Zen3 CPU。

AMD提供了更多细节,确认该技术将用于Zen3的CPU,更具体地说是Ryzen CPU。CPU将在今年晚些时候生产,因此我们可以期待在2022年初会推出。 距离AMD转换到Zen4还有至少两个季的时间。但AMD没有说明这些是桌上型还是行动处理器会採用,但从外观上看桌上型Ryzen CPU更有可能发生。AMD将专注于代号为 Rembrandt的下一代Ryzen APU,据传将採用新的Zen3+核心,而Ryzen桌上型CPU将重用现有的Zen3核心并增加3D V-Cache。

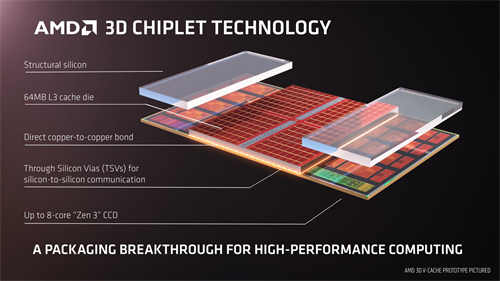

单3D V-Cache堆栈包含64MB的L3快取,使用在现有Zen3 CCD之上。快取将增加在增加现有的32MB L3 ,每个CCD总共有96MB。所以将包括每个小晶片1个3D V-Cache堆栈,因此我们可以看到顶级Ryzen SKU上总共会有192MB的快取。但是AMD表示V-Cache堆栈可以达到8-hi,这意味着除了每个Zen3 CCD 的32MB快取之外,单个CCD在技术上还可以提供高达512MB的L3。

AMD已经精简了Zen3 CCD和V-Cache,因此它们的高度与当前的Zen3处理器相同,而不是核心和IOD之间的高度不同。由于V-Cach位于CCD L3快取的顶部,因此它不会影响核心的热量输出。AMD还展示了其採用小晶片架构CPU的下一代3D堆叠设计。该技术预计将多个IP堆叠在一起,但AMD展示的原型包括带有3D V-Cache和64MB L3 SRAM的 Ryzen 9 5900X。

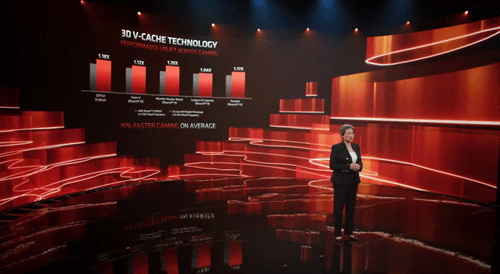

该原型拥有一个标準Zen3 CCD,旁边是一个3D封装的CCD,其尺寸为6mmx6mm (36mm2)。CCD的大小与以前相同,但在CCD之上还有另一个封装,它有64 MB快取,增加了Zen3 CCD上已有的32MB L3快取。AMD甚至展示了这个原型,这意味着该技术确实有效,而不仅仅是纸上展示。Ryzen 9 5900X原型执行Gears V,由于增加了游戏快取大小,性能提高了12%。平均而言AMD声称透过3D V-Cache设计提高了15%的性能。每个V-Cache堆栈提供高达2TB/s的总频宽。

Multiple Reboot Scheduler(系统优化工具)

460KBM

下载

VIPRE Internet Security(互联网安全保护工具)

40.3MM

下载

28.48M

下载