目前高科技产品都离不开「心脏」——晶片,但是目前电子产品更新速度越来越快,而与之相反的是晶片的迭代周期开始跟不上。为了能够保证晶片的快速迭代,必须缩短设计週期。

Google 团队为了缩短晶片设计週期,将 AI 强化学习方法运用其中,EDA 巨头 Synopsys 和 Cadence 也是推出了类似的工具。

目前 AI 晶片的开发需要投入大量资金和时间,通常需要几年的时间完成研发,难以满足 AI 算法更新需求。为了这个矛盾,Google 做了一个大胆的决定,让 AI 来设计 AI 晶片。

在 Arxiv 网站上有一篇论文称「我们相信,AI 将能够缩短晶片的设计週期,在硬件与 AI 算法之间建立共生关係,并进一步推动彼此的进步。我们已经看到,有些算法或神经网络架构在现有的 AI 加速器上效果不佳,因为加速器设计类似于两年前,而那时这些神经网络架构和算法并不存在。」还有 Google 高级研究科学家 Azalia Mirhoseini 称「如果缩短设计週期,我们可以缩小差距。」

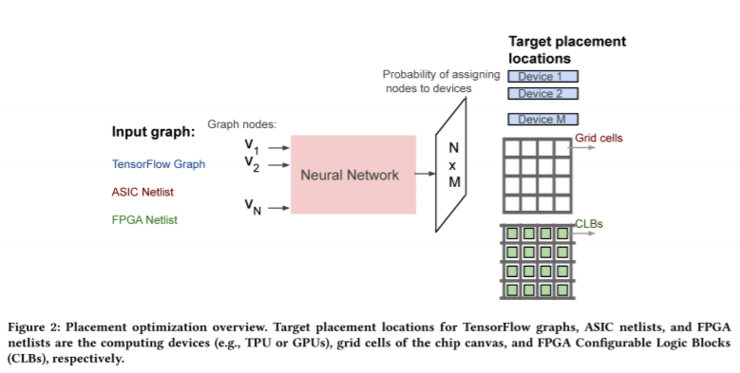

晶片开发最耗费时间的是「布局」,Mirhoseini 和高级软件工程师 Anna Goldie 提出了一个神经网络,是通过对晶片的长时间学习,使其能够在 24小时内设计好 Google Tensor 处理单元,并且在功耗、性能、面积上超过了专家数週的研究成果。

值得注意的是,Goldie 和 Mirhoseini 的 AI 布局建模为强化学习问题,不是通过大量数据来进行训练学习,而是让 AI 边做边学习。这样设计的好处是能够有效调节参数,降低功率等,并且随着设计的越多,呈现的效果会更好。

两大 EDA 公司也推出了相应的工具。 Synopsys 的自主 AI 晶片设计程式 DSO.ai(Design Space Optimization AI)。是通过晶片设计产生大数据流,随着时间演变,调整设计,让设计向多维优化目标发展。 Cadence 为新版 Cadence 数码全流程,支援机器学习(ML)功能,实习统一布局布线和物理优化引擎等多项业界首创技术,在吞吐量上最高提升 3倍,PPA 最高提升20%。

随着 AI 技术的发展,不知道还会带来什么样的便捷,真是科技改变生活。

云骑士一键重装系统